#### **Features**

- Two-Chip PC/AT Compatible Chip Set for 80386DX Systems Operating up to 40 MHz

- AT40391B System and Cache Controller AT40392 Data Buffer Controller

- Two 160-Pin Quad Flatpacks

- On-Chip Support for Direct-Mapped Write-Back Cache

- 0 Wait State Cache Read Hit and Programmable 0/1 Wait State Cache Write Hit

- Two Programmable Non-Cacheable Regions

- On-Chip Tag Comparator

- Burst Line Fill During Cache Read Misses

- Page Mode Main Memory Operation with Programmable Wait States Supporting Platform Memory Sizes up to 64 Mbytes

- Support for 256K, 1-Mbit and 4-Mbit DRAMs

- Low Power CAS# Before RAS#, Transparent DRAM Refresh

- Low Power, Slow Refresh for Laptop PC Operation

- Parity Generation and Detection

- Support for Shadow RAM

- Cacheable Video BIOS Option

- 8042 Emulation for Fast CPU Reset and Gated A20 Generation

- ISA Bus Control with Programmable Clock

- 0 or 1 Wait State for 16-Bit ISA Bus Cycles

- Support for 80387DX and 3167 Numeric Co-processors

**Block Diagram** CPU Peripheral Peripheral ISA Data Data Address Address Rus Rus Rus Rus CPU ISA Address Data Bus MD Bus AT40206 BIOS Integrated Peripheral Controller 80387DX Numeric Co-processor AT40392 Keyboard **DATA BUFFER** Controller CONTROLLER 80386DX CPU  $\triangleright$ TAG RAM 4 CACHE RAM AT40391B  $\triangleright$ STEM AND CACHE 4 CONTROLLER D DRAM 4

80386DX PC/AT Chip Set

9-3

**■ 1**074177 0005718 70T ■

**AIMEL**

### Description

The Atmel AT40391B/AT40392 chip set is a 100% IBM PC/AT compatible chip set for 80386DX based systems operating up to 40 MHz. The high integration and an on-chip writeback, direct-mapped cache controller design allows maximum system performance. Together with a peripheral controller, such as the AT40206 integrated peripheral controller, a very high performance, yet low cost, 80386DX motherboard can be built with a minimum number of components.

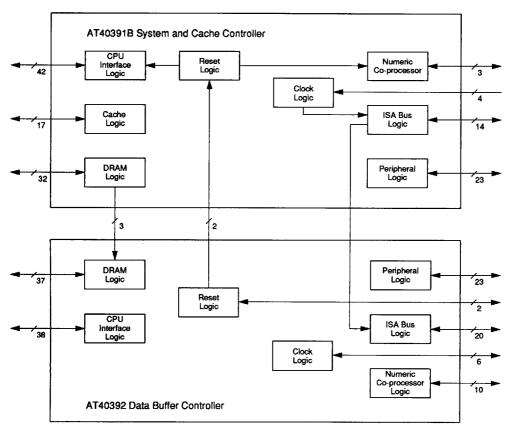

The AT40391B system controller performs the system control, memory and cache control functions. The system control logic consists of the following logic blocks: CPU control, AT bus cycle control, numeric co-processor control, synchronous clock circuitry and peripheral bus control. The memory and cache controller functions consist of a write-back, direct-mapped cache controller and a paged mode DRAM controller. The AT40391B supports cache sizes up to 256 Kbytes (16-byte line size), and platform memory sizes up to 64 Mbytes.

The AT40392 data buffer controller performs the data buffer and co-processor interface functions. The data buffer logic performs bus conversion logic for various 8-, 16- and 32-bit data movements as required among the system buses. The other functions of the AT40392 are co-processor interface, keyboard controller decoding, reset and generation of various peripheral clocks.

Low cost systems are made possible through the support of single ROM/EPROM BIOS configurations. The BIOS ROM/EPROM can be either 8-bit or 16-bit. DRAM is located on the system platform bus, thus reducing DRAM speed requirements by at least 15 ns.

The AT40391B/AT40392 PC/AT chip set is compatible with the AT40206 integrated peripheral controller and works with BIOS from AMI, Phoenix, Award and Quadtel.

### **Functional Block Diagram**

AT40391B/392

**1**074177 0005719 646

9-4

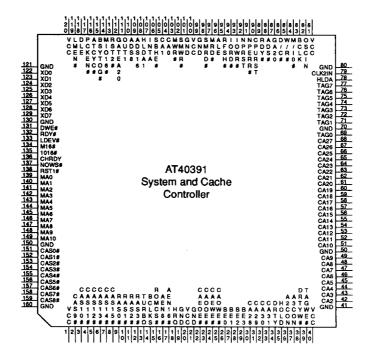

#### AT40391B System and Cache Controller

- Programmable clock generators for the platform and ISA buses

- CPU and numeric co-processor reset control

- Direct-mapped write-back cache controller

- 0 wait state cache read hit and programmable 0/1 wait state cache write hit

- · Two programmable non-cacheable regions

- Cacheable video BiOS option

- On-chip tag RAM comparator

- Burst line fill during cache read misses

- Programmable page mode DRAM controller for 256K, 1-Mbit, and 4-Mbit DRAMs for platform memory sizes up to 64 Mbytes

- Decoupled system platform and ISA bus DRAM refresh

- Low power CAS# before RAS#, transparent DRAM refresh

- · Slow refresh option

- Shadow RAM support

- Programmable 0/1 wait state for ISA bus cycles

The Atmel AT40391B is a highly integrated system and cache controller for 25 MHz, 33 MHz and 40 MHz 80386DX PC/AT systems. When combined with the AT40392 data buffer controller and the AT40206 integrated peripheral controller, a powerful but low cost PC/AT can be built with minimal components.

The AT40391B performs all the system control, memory control, cache control, and bus arbitration functions for an 80386DX PC/AT system including the reset and power shutdown functions and synchronous CPU and ISA bus clocks generation. The flexible memory controller supports system memory sizes up to 64 Mbytes with a wide range of DRAMs. The direct-mapped write-back cache controller implements a high performance cache system while requiring minimal external components. The functions of the AT40391B are programmed through twelve configuration registers.

## **Pin Configuration**

9-5

1074177 0005720 368

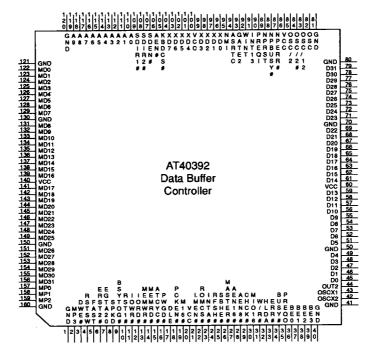

#### AT40392 Data Buffer Controller

- Data bus conversions

- DRAM parity generation and detection

- ISA bus direction control

- Reset logic

- Peripheral clock generation

- Keyboard and real-time clock chip select

- Speaker control

- . PortB, 70H and NMI logic

- · Numeric co-processor interface

- Keyboard reset and Gate A20 emulation logic

The Atmel AT40392 is a highly integrated data buffer controller for 25 MHz, 33 MHz and 40 MHz 80386DX based PC/AT systems. Together with the AT40391B system and cache controller and the AT40206 integrated peripheral controller, a low cost yet powerful PC/AT can be built with minimal components.

The AT40392 data buffer controller performs all of the data buffering control required in a 386DX PC/AT system. Under the control of the CPU and the AT40391B system and memory controller, the AT40392 routes data to and from the CPU bus, MD bus, XD bus and the ISA bus, while also providing any necessary data size conversions. The AT40392 also performs high byte to low byte and low byte to high byte swapping on the ISA bus. For platform DRAM accesses, the AT40392 performs parity error checking and generation.

### **Pin Configuration**

AT40391B/392

| 1074177 0005721214 🖪

9-6

# **Ordering Information**

| CPU Clock<br>(MHz) | Power<br>Supply | Ordering Code             | Package      | Operation Range             |

|--------------------|-----------------|---------------------------|--------------|-----------------------------|

| 25                 | 5 V ± 5%        | AT40391B-25<br>AT40392-25 | 160Q<br>160Q | Commercial<br>(0°C to 70°C) |

| 33                 | 5 V ± 5%        | AT40391B-33<br>AT40392-33 | 160Q<br>160Q | Commercial<br>(0°C to 70°C) |

| 40                 | 5 V ± 5%        | AT40391B-40<br>AT40392-40 | 160Q<br>160Q | Commercial<br>(0°C to 70°C) |

| Package Type |                                                      |  |

|--------------|------------------------------------------------------|--|

| 160Q         | 160 Lead, Plastic Gull Wing Quad Flat Package (PQFP) |  |

9-7

■ 1074177 0005722 130 ■